# An Out-of-band Approach to SAN-level Cache Management

Da Xiao Wei Xue Jiwu Shu Weimin Zheng

Dept. of Computer Science & Technology Tsinghua University, 100084 Beijing, China xiaoda99@mails.tsinghua.edu.cn

Tsinghua University

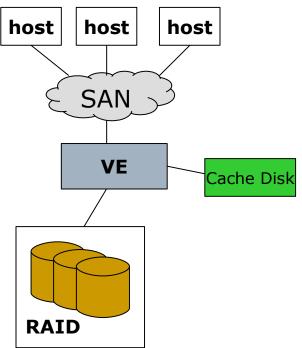

## SAN-level cache

- Maintains "globally hot data blocks" in the cache disk to boost SAN performance

- SAN-level vs. localized cache

- Exploits global storage access information to cache more valuable blocks

MSST'06

Scales the size easily

### Motivation

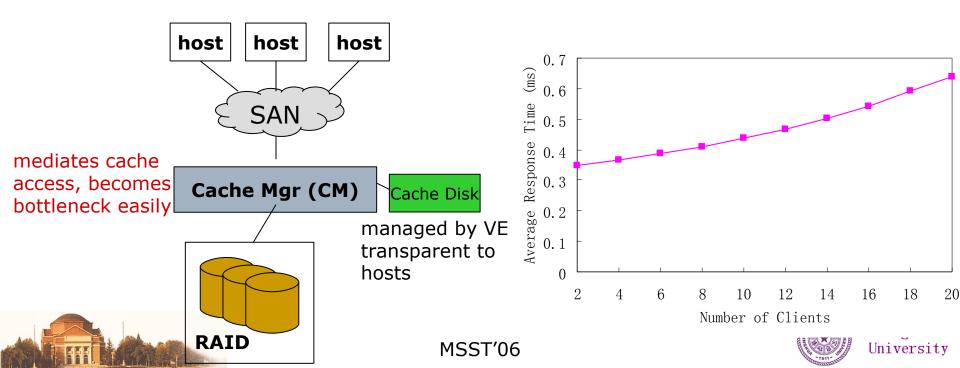

#### In-band SAN Level Cache

- Gets global access information easily

- Poor scalability. The performance improved by cache will suffer with the increase of hosts

## Motivation

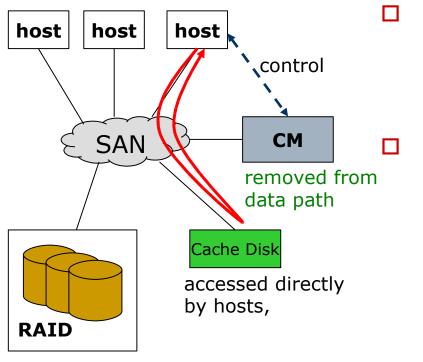

#### Out-of-band SAN Level Cache

- Out-of-Band Architecture is more Scalable

- SAN Level Cache based on Out-of-Band Architecture

- How to implement

- How to perform the place/replace cache?

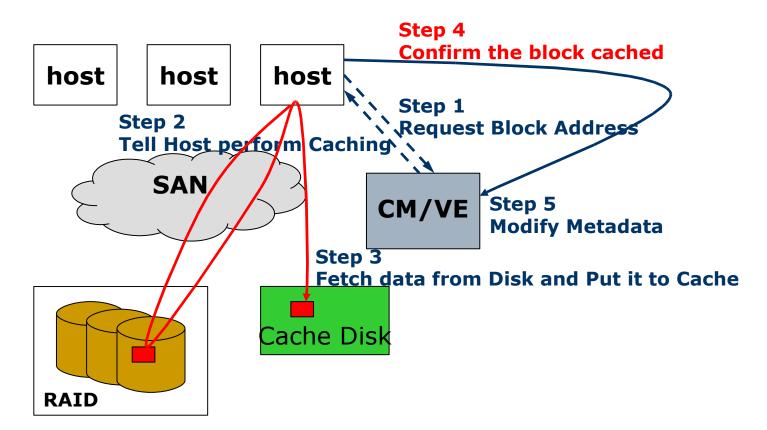

## Out-of-Band SAN level Cache

Example: Cache Miss and Placement/Replacement

#### Cache Placement and Replacement

- Release the overhead introduced by replacement of out-of-band SAN cache

- Access and Cache Queue algorithm (ACQ)

- Which is Cache Candidate

- The request block is the candidate

- Only the identifiers and reference counts of recent access blocks are recorded in Access Queue, replacing by LRU policy.

- Which in cache will be replaced

- Cache Queue keeps ids and reference counts of the cached blocks

- The block with the least RC in CQ --- Threshold

- When replace take load rate into account

- RC of request block in AQ > the least RC in CQ

#### Cache Placement and Replacement

#### Comments

- Well cache space usage is achieved in most cases

- threshold changes according to the state of cache

- Load rate is reduced compared with demanding caching, such as LRU

Only part of request blocks enter into cache

- Fit well to the Second level cache access pattern

MSST'06

Algorithm based on access frequency

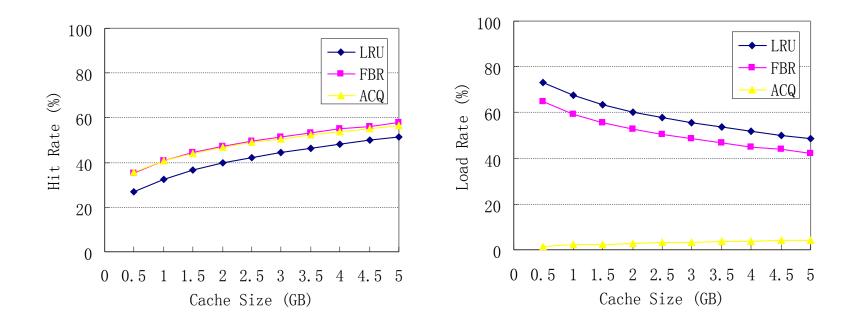

#### Simulation results – cache hit and load rate

ACQ is close to FBR (<1.5%)</p> ACQ is more than 90% lower than FBR

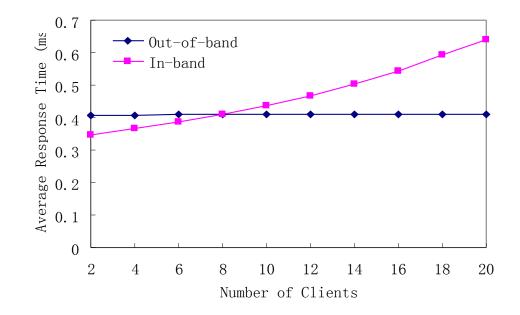

#### Simulation results – Performance and Scalability

Average Response Time using ACQ of out-of-band compared with FBR of in-band less when host number > 10 increase much slower

# Thank you! http://storage.cs.tsinghua.edu.cn