# Computational Storage A Standards Update

Scott Shadley SNIA Executive BoD SNIA CMSI GB NVM Express Member Solidigm Long-Term Strategy

**SNIA**

Presented at MSST - SCU - 2023, on behalf of SNIA and NVM Express Working Groups

1

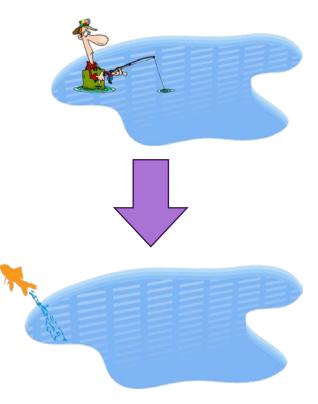

# The Evolution of Compute

Why Now for Compute Beyond the CPU

## A Quick Recap of Why We Are Here

#### Why Now?

- Storage is no longer 'SLOW'

- Memory is no longer 'Gated'

- Data Gravity, Data Size, Data Locality

- Edge Data Explosion, Transport issue!

- SNIA, NVMe, CXL, OCP, Others are providing new guidance in new areas of implementation

# Key Benefits? Faster, Fewer, Easier I/O transfers Reducing DRAM/Network tax with new transports, solutions, products

- Redeploy Primary CPU to High Value Work, offer up new services to help

- Improved performance due to parallelism for certain workloads

- Better scheduling of data management and device functionality

#### SNIA Architecture and API, NVM Express Command Infrastructure

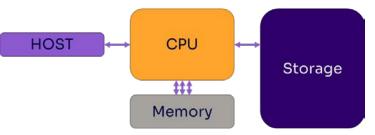

#### John von Neumann – The Princeton Architecture

The Ecosystem today, we have our friend J. v N. - CPU/Memory/Storage

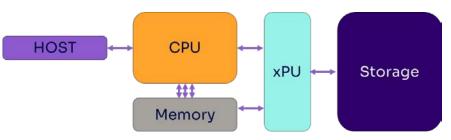

The world is evolving and there is a need for compute in more available locations, enter the world of "Accelerators" – SmartNIC, xPU, DPU, GPU, IPU

• These are great, but there is <u>room for more</u>! History tells Us this much...

# Standardizing Computational Storage

On Behalf of the CS TWG Co-Chairs:

Bill Martin Jason Molgaard

**SNIA**<sup>®</sup>

## The Continued Growth of Experience

- CS TWG is continuing to see growth

- **48** companies, **258** individual members

- Work within SNIA Efforts

- **CS SIG** Webinars, Blogs, Events

- SDXI Sub-Group Collaboration

- Security TWG Addressing Security

- Collaborating with External Groups

- **NVM Express** Computational Programs

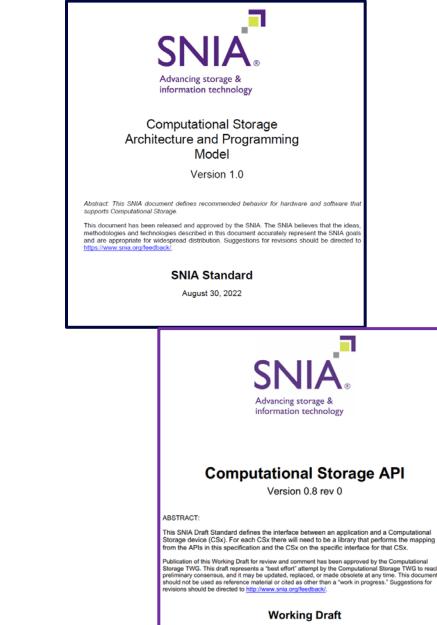

## Current Progress of TWG Output

- Architectural Document v1.0 has been released

- v1.1 under development

- Security enhancements for multiple tenants

- Chaining of Commands

- Expansion of use cases

- API v0.8 public review version also available

- <u>API v1.0 under development</u>

- Abort/reset handling

- Device Memory

- NVMe Computational Programs support

- Other Miscellaneous Updates

June 29, 2022

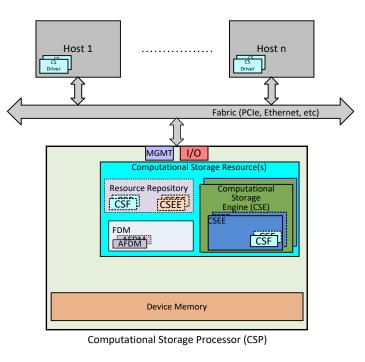

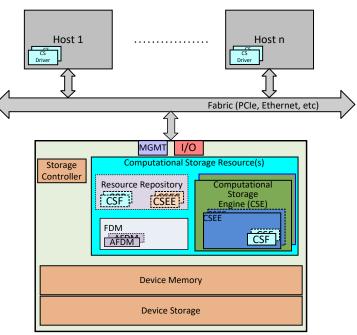

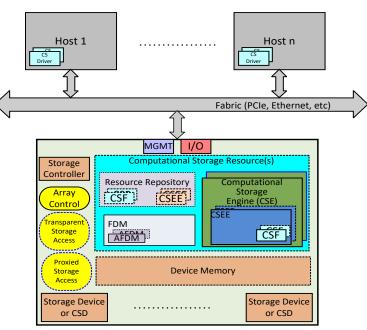

#### Computational Storage Architecture

Computational Storage Processor

Computational Storage Drive

Computational Storage Drive (CSD)

Computational Storage Array

Computational Storage Array (CSA)

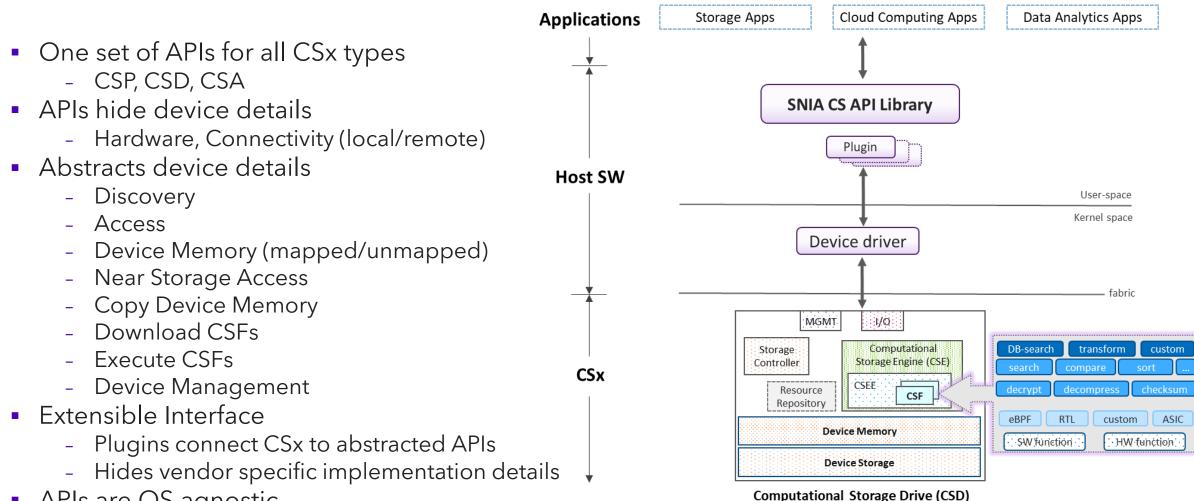

CSx = Computational Storage Device – CSP or CSD or CSA

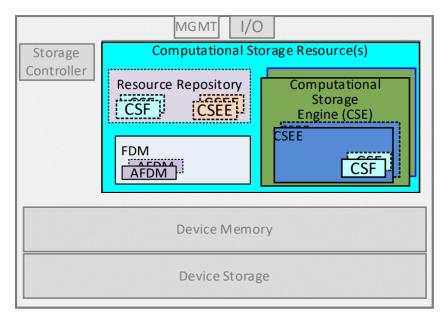

## Deep Dive of the CSx Resources

Computational Storage Drive (CSD)

#### **SNIA Dictionary - CS Terms**

**CSR** - Computational Storage Resources are the resources available in a CSx necessary for that CSx to store and execute a CSF.

**CSF** - A Computational Storage Function is a set of specific operations that may be configured and executed by a CSE in a CSEE.

**CSE -** Computational Storage Engine is a CSR that is able to be programmed to provide one or more specific operation(s).

**CSEE -** A Computational Storage Engine Environment is an operating environment space for the CSE.

**FDM -** Function Data Memory is device memory that is available for CSFs to use for data that is used or generated as part of the operation of the CSF.

**AFDM -** Allocated Function Data Memory is a portion of FDM that is allocated for one or more specific instances of a CSF operation.

# API Use In Computational Storage

On Behalf of the CS API Lead Editors:

Oscar Pinto

Bill Martin

Presented at MSST - SCU - 2023, on behalf of SNIA and NVM Express Working Groups

## SNIA Computational Storage APIs

• APIs are OS agnostic

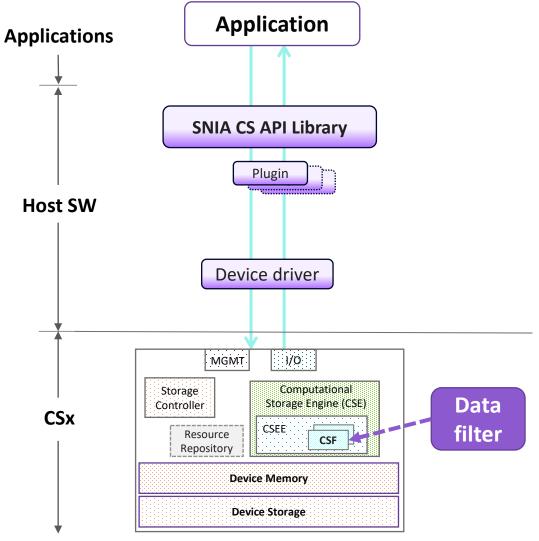

## Example Use Case - Abbreviated

- Execute Data Filter CSF

- Allocate Device Memory (FDM)

- Load Data from Storage

- Run Data Filter CSF on loaded Data

- Copy Results to Host Memory

**Computational Storage Drive (CSD)**

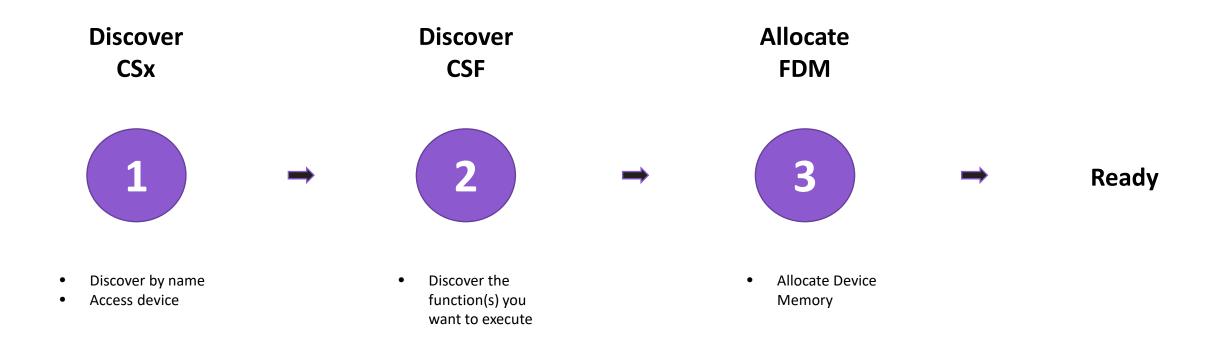

## Prepare for Computational Storage (Setup)

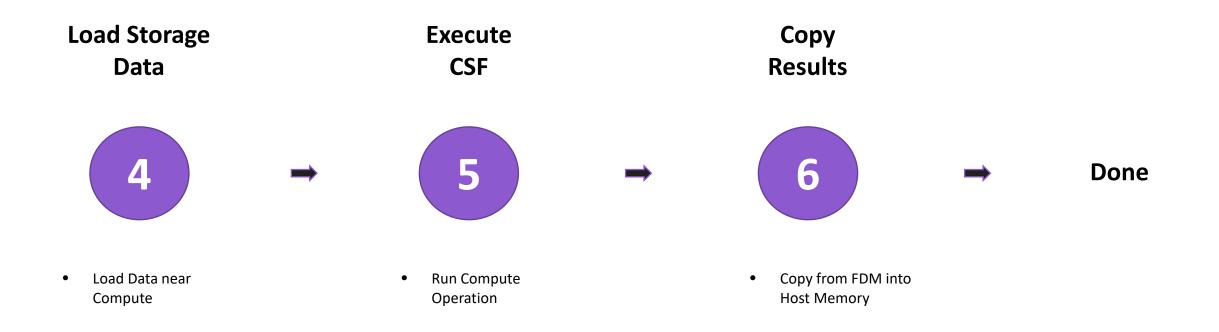

## Perform Computational Storage I/O (Run)

## Usage Summary

csGetCSxFromPath("my\_file\_path", &length, &csxBuffer); csOpenCSx(csxBuffer, &MyDevContext, &devHandle);

3

csGetCSFId(devHandle, "filter", &infoLength, &count, &csfInfo);

csAllocMem(devHandle, CHUNK\_SIZE, &f, &afdmHandle1, NULL);

csQueueStorageRequest(storReq, storReq, NULL, NULL, &compVal);

csQueueComputeRequest(compReq, compReq, NULL, NULL, &compVal);

csQueueCopyMemRequest(copyReq, copyReq, NULL, NULL, NULL, NULL);

# Bridging the Gap Architecture to Implementation

## Correlation of SNIA/NVMe terms

### **SNIA Terms**

- Computational Storage Engine (CSE)

- Computational Storage Engine Environment (CSEE)

- Resource Repository

- Downloaded CSF and CSEE

- Pre-loaded CSF and CSF

- Activation

- Function Data Memory (FDM)

- Allocated FDM (AFDM)

- Device Storage

#### **NVMe Terms**

- Compute Namespace

- Virtual (Not currently defined)

- Programs

- Downloaded programs

- Device-defined programs

- Activation

- Subsystem Local Memory (SLM)

- Memory Range

- NVM Namespaces

## Differences between SNIA and NVMe

#### SNIA

- Defines CSEE

- CSF can directly access

AFDM or Storage

- Supports an indirect model

#### **NVMe**

- CSEE is logical no specific definition

- Program has access to Memory Range Set

- Specific Execute command only

# A Look at the NVMe Implementation

On Behalf of the NVM Express Computational Storage Task Group:

Bill Martin Kim Malone

Presented at MSST - SCU - 2023, on behalf of SNIA and NVM Express Working Groups This presentation discusses NVMe<sup>®</sup> technology work in progress, which is subject to change without notice.

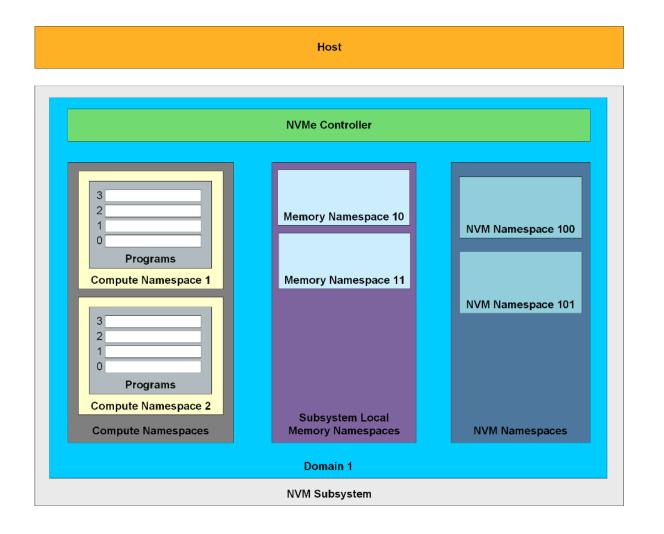

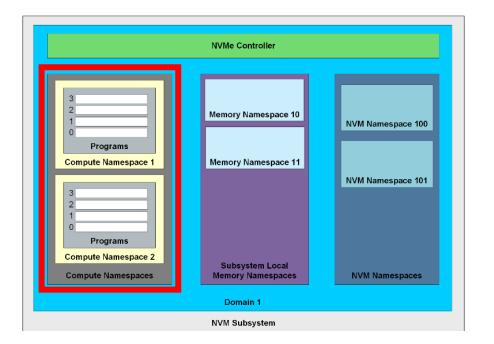

## NVMe Major Architectural Components

The NVM Express<sup>®</sup> (NVMe<sup>®</sup>) computational storage architecture involves several types of namespaces:

- Compute namespaces (new)

- Memory namespaces (new)

- NVM namespaces

- NVM, Zoned, and Key Value namespaces

Presented at MSST - SCU - 2023, on behalf of SNIA and NVM Express Working Groups This presentation discusses NVMe<sup>®</sup> technology work in progress, which is subject to change without notice.

## **Compute Namespaces**

A compute namespace:

- Is a namespace in an NVMe technology subsystem that is able to execute one or more programs

- Is a namespace that is associated with the Computational Programs I/O command set

- Contains compute resources

#### **TP4091: Computational Programs**

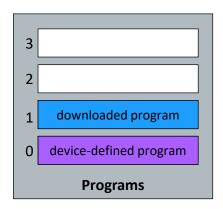

## New Computational Programs I/O command set for compute namespaces

- New commands include:

- Execute program

- Load program

- Activate program

- Create/Delete Memory Range Set

- Provides log pages for program discovery

#### **Computational Programs**

- Conceptually similar to software functions

- Called with parameters and run to completion

- Are addressed via a compute namespace program index

- May be identified by a globally unique program identifier

- Operate only on data in Subsystem Local Memory

- May be device-defined or downloadable

- Device-defined programs

- Programs provided at time of manufacture e.g., compression, encryption

- Downloadable programs

- Programs that are loaded to a Computational Programs namespace by the host

- A program may only be able to execute on a subset of the compute resources in an NVM subsystem

- A program may be implemented in an ASIC

- A program may be executed on a CPU core

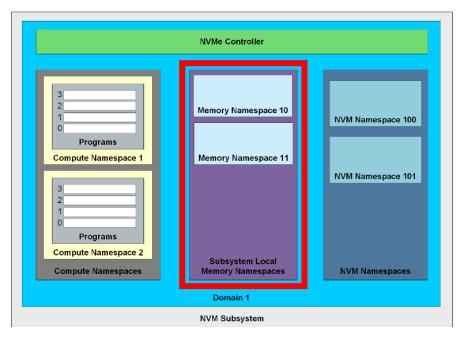

## Memory Namespaces

A memory namespace:

- Is a namespace in an NVMe technology subsystem that provides host command access to memory in the NVMe technology subsystem

- Is a namespace that is associated with the Subsystem Local Memory I/O command set

- Is used by the Computational Programs command set to provide access to SLM for program execution

#### TP4131: Subsystem Local Memory (SLM)

New Subsystem Local Memory I/O command set for memory namespaces

- New commands include:

- Memory read and memory write

- Commands for transferring data between host memory and a memory namespace

- Memory copy

- Command for copying data between NVM and memory namespaces

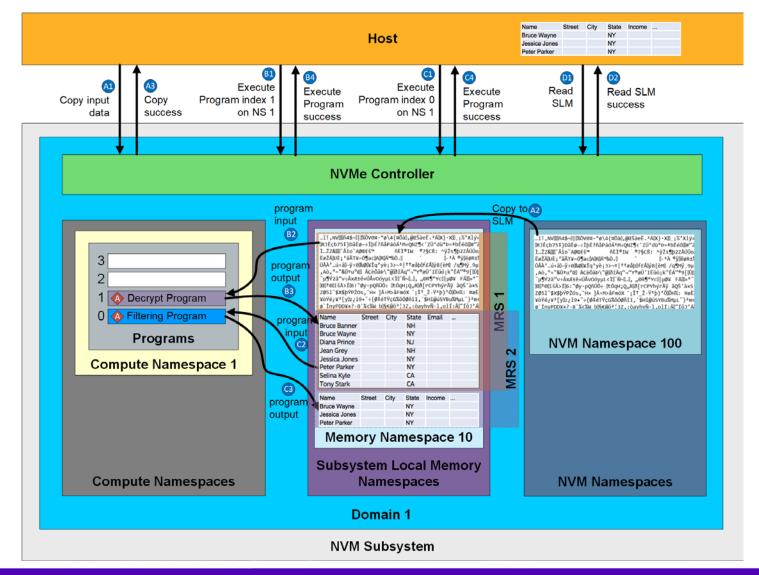

## Flow: Execute Program - Filter Encrypted Data

#### Precondition:

Memory Range Sets MRS1 and MRS2 have been created

#### Flow steps

- A Copy encrypted data into SLM

- B Execute Program 1 on compute NS 1 using MRS1

- C Execute Program 0 on compute NS 1 using MRS2

- Read filtered data from SLM to host

Presented at MSST - SCU - 2023, on behalf of SNIA and NVM Express Working Groups This presentation discusses NVMe<sup>®</sup> technology work in progress, which is subject to change without notice.

## What's Next?

How Can You Help!

**SNIA**<sub>®</sub>

# Help Progressing Computational Storage

- Join the SNIA Technical Work Group

- Go to SNIA Member Portal

- Select <u>TWG: Computational Storage</u>

- Click on the "Join Group"

- CS TWG meetings

- Wed 10-11am Pacific time

- Join the task group

- Go to the NVMe workgroup portal

- Select the <u>CS Task Group</u>

- Click on the "Join Group" link

- Task group meetings

- Thursdays 9-10am Pacific time

## Thank you Scott.Shadley@Solidigm.com

Presented at MSST - SCU - 2023, on behalf of SNIA and NVM Express Working Groups

27